안녕하세요!

SPTA 반도체공정기술교육원

6.3부터.

최대한 오래 기억하고 싶어 각 기여는 코스 당일에 작성되며 편집 과정이 완료된 후 업로드됩니다!

코스별로 정리하면 좋을 것 같아서 다음 글부터 각 코스의 제목별로 정리하도록 하겠습니다.

Day 1) Poly-Si LPCVD까지 제조 전 과정에 대한 이론 수업 및 실습

< Theorieunterricht >

먼저 제 소개를 했습니다.

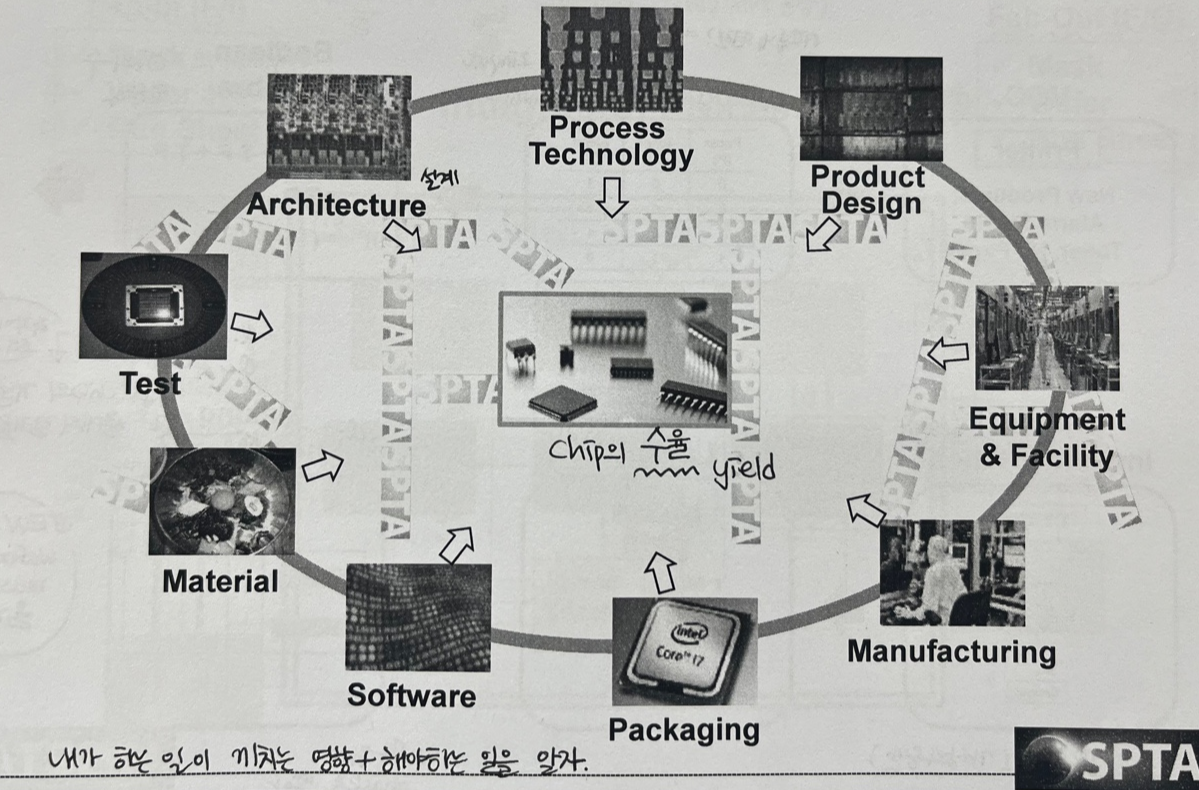

그리고 반도체 생태계 Eco System @Semiconductor Industry를 알게 되었습니다.

목표는 칩 수율과 수율을 향상시키는 것입니다.결과적으로 많은 활동이 반도체 생태계를 형성합니다.

교수 “내가 하고 있는 일과 해야 할 일이 의미하는 바를 인식하십시오.”그리고 팁을 주셨어요.

반도체 IC 흐름은 다음과 같습니다.

칩 설계 -> 제조 -> 테스트 및 패키징

칩 디자인VOC, 회로 설계, 레이아웃 및 EDA 도구를 사용한 활동이 포함됩니다.

이 디자인은 Photo Mask로 가능합니다. 조작것이 가능하다.

제조 단계는 클린룸, 공정 도구, 통합 공정, FEOL+BEOL 및 웨이퍼 레벨을 보여줍니다.

그리고 처리된 웨이퍼를 통해 T테스트 및 패키지계속하려면.

전기 테스트, EDS, 와이어 본딩에 대한 웨이퍼 박막화 및 패키지 레벨이 이 단계에서 수행됩니다.

패브리케이션 부문에서는 삼성이, 테스트앤패키지 부문에서는 TSMC가 1위를 차지했다.

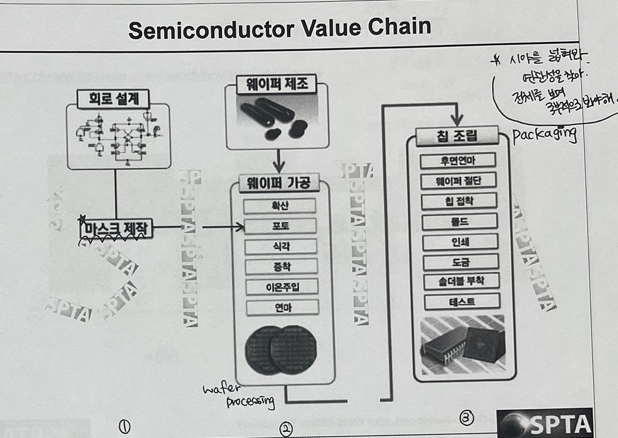

반도체 밸류 체인을 살펴보면,

①마스크, ②웨이퍼 가공, ③칩 패키징의 3단계로 구성할 수 있습니다.

IC 제조에서는 Fab-In(F/I) 및 Fab-Out(F/O)이라는 용어가 사용됩니다.

팹인 마스크패턴 와플~ 위에 런닝 시트를 기반으로 제작되었습니다.

이것은 “반도체 = 콘도미니엄”으로 표현할 수 있습니다.

청사진을 가지고 땅에 차곡차곡 쌓이는 선을 따라가는 것이라고 할 수 있다.

팹 아웃하면 위의 세 가지가 나옵니다.

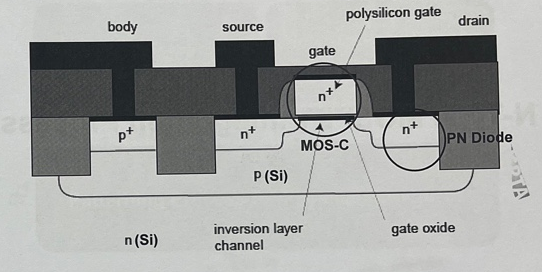

마지막으로 MOSFET에 대해 간략하게 살펴보았습니다.

MOSFET의 정의는 다음과 같습니다.

1. 게이트 아래에는 게이트 전압에 따라 달라지는 반전층이 있습니다.

2. 그리고 이 영역은 고농도 도핑 영역으로 소스와 드레인이 연결되어 있습니다.

3. 게이트, 소스, 드레인, 바디 4개의 단자로 구성되어 있습니다.

기기를 바라볼 때 top view와 vertical view를 함께 이해하면 좋습니다.

MOSFET은 이름으로도 정의됩니다.

MOS/FE/T – MOS: 금속 산화물 반도체 구조 기반

– FE: 작동의 기본 원리로 전계 효과가 있는 전기적 중성

– T: 전압에 따라 저항이 변하는 트랜지스터 소재

내가 나중에 쓸 포스트는 내꺼야 글을 정리하는 데 사용나는 간단한 문장을 만들고 쓰려고 노력한다

면접을 준비하면서 모든 단어를 말로 설명하려고 노력하겠습니다!

빠진 것이 있으면 알려주세요, 감사합니다!